# European Chips Act State of Play and Outlook

Arian Zwegers Microelectronics and Photonics

18 February 2025

### **Chips Act**

European Semiconductor Board (Governance)

| Pillar 1                                                                                                                                                      | Pillar 2                                                                        | Pillar 3                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chips for Europe<br>Initiative                                                                                                                                | Security of Supply                                                              | Monitoring and Crisis<br>Response                                                                                                                       |

| <ul> <li>Initiative on<br/>infrastructure building in<br/>synergy with the EU's<br/>research programmes</li> <li>Support to start-ups and<br/>SMEs</li> </ul> | <ul> <li>First-of-a-kind<br/>semiconductor<br/>production facilities</li> </ul> | <ul> <li>Monitoring and alerting</li> <li>Crisis coordination<br/>mechanism with MS</li> <li>Strong Commission<br/>powers in times of crisis</li> </ul> |

Innovation policy

Industry policy

+

Crisis management strategy

+

#### Pillar I – Chips for Europe Initiative Infrastructures open to a wide range of EU users

#### 5

Pilot lines

launched Prototyping of validated designs Testing of equipment Validation of process flows

**Competence centres**

Access to technical expertise, helping companies to approach and improve design capabilities and developing skills

#### In 25 countries, more coming

#### **Design Platform**

Help designing semicorrogress devices, via access to Electronic Design Automation tools and IP libraries

#### Quantum chips

In

Technology and engine progress capacities for accelerating innovative development of quantum chips

Various topics in Chips JU WP2025 address the Initiative

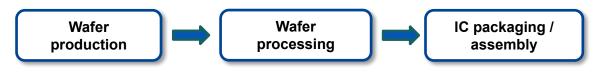

## Pillar II – Security of supply

**First-of-a-kind facility (FOAK):** offers innovation in terms of products or process (e.g. environmental performance) <u>not yet present in</u> <u>the Union</u>

Planned investments by major manufacturers exceeding EUR 80 Billion

The Commission *approved* State aid for the following projects so far:

|                                                                           | Company                         | MS   | Location | Investment<br>(EUR Billion) | Technology         |  |

|---------------------------------------------------------------------------|---------------------------------|------|----------|-----------------------------|--------------------|--|

| <b>A</b> 77                                                               | ST Microelectronics             | IT   | Catania  | 0.73                        | SiC wafer          |  |

| <b>∽</b> 7 <b>∯</b>                                                       | ST Micro & GlobalFoundries      | FR   | Crolles  | 7.5                         | 300-mm FD-SOI      |  |

| <b>A7</b> /                                                               | ST Microelectronics             | IT   | Catania  | 5                           | SiC devices        |  |

| BOSCH NP                                                                  | ESMC (JV<br>TSMC+Bosch/IFX/NXP) | DE   | Dresden  | >10                         | CMOS, FinFET       |  |

| More pr                                                                   | Silicon Box                     | nced | Novara   | 1.3                         | Advanced packaging |  |

| Further, IPCEI ME-CT started in 2023 with over EUR 21 Billion investments |                                 |      |          |                             |                    |  |

All stages of semiconductor production are eligible

## Pillar III – Monitoring and crisis management

Anticipating and mitigating shortages of the semiconductor supply chain

Strengthening the Union's and Member States' **abilities to react to crises** related to disruptions of the semiconductor supply chain

#### Pillar III work strands:

- Analysis of supply chains, choke points, dependencies for chips (e.g. legacy chips) and raw materials (e.g. Gallium, Germanium)

- **Data collection** (*MS*, *JRC*, *think tanks*, *market reports*)

- Mapping of Key Market Actors with Member States

- Organisation of crisis management with MS and

**Emergency Toolbox** which the Commission is empowered to use to **ensure security of supply to critical sectors** in the crisis stage:

| @ <b>1</b> .  | Information<br>gathering | <u></u> 2. | Priority rated orders |

|---------------|--------------------------|------------|-----------------------|

| <b>;;; 3.</b> | Common<br>purchasing     | <b>4.</b>  | Export<br>control     |

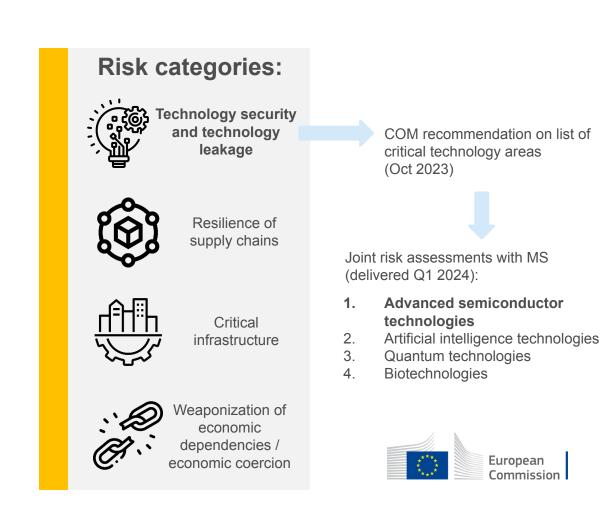

# Outlook

# **Economic Security**

- Joint Risk Assessments with MS, including in semiconductors

- Monitoring "mainstream chips" investments in third countries

- Analysis of dependencies on raw materials, e.g. Gallium, Germanium

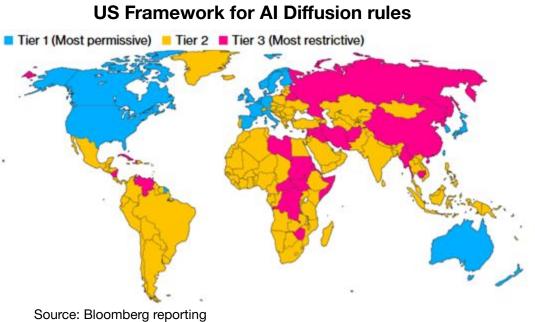

- Analysis of US Al diffusion rules (see next slide)

Chips JU WP2025 topics

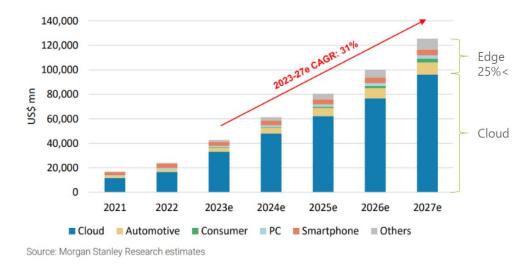

# AI Chips

- Booming Al market to drive substantial semiconductor growth

- EU industries (automation, telecom, aerospace, defence) will require fine-tuning of AI models with own proprietary data

- Biden's Framework for AI Diffusion rules go against EU Single Market and AI ambitions

- EU cannot just rely on US HW+SW

- High risk of vendor lock-in and technology dependence

- EU has strong R&D competences and innovative startups in low-power embedded AI, but lack of funding leads to brain-drain

#### Chips JU WP2025 topics

Low-power Edge AI Chips (20 M€)

#### Beyond 2025??

Note: Mapped data show level of restrictions on chip shipments for distinct

# International Cooperation, Skills

- G7 🚺 • Multilateral engagement: G7, OECD, GAMS

- International cooperation on semiconductors

- TTC with US, India

Digital Partnerships with Japan, Korea, Singapore, and Canada •

#### Skills

European Chips Skills Academy, vocational training (upskilling/re-skilling)

#### Chips JU WP2025 topics

- Boosting R&I cooperation between EU and Japan on semiconductors (1 M€)

- A Pan-European infrastructure for Chips Design Innovation (12 M€)

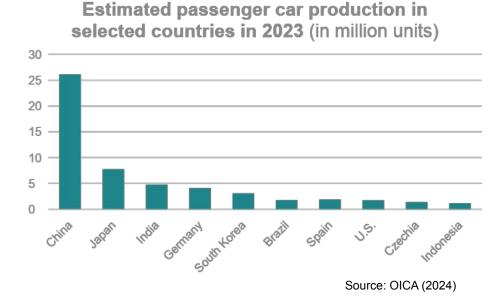

# Automotive

- Competitiveness Compass announces Strategic Dialogue on future of European automotive industry and Industrial Action Plan

- Addresses challenges around innovation and leadership in future technologies

- Working Group under Alliance

#### Chips JU WP2025 topics

- Heterogeneous integration for high-performance automotive computing (20 M€)

- RISC-V Automotive Hardware Platform (80 M€)

# Chips Act review

Chips Act review due by September 2026

- To identify trends and define future needs/priorities, need to consult and involve closely:

- o Member States (ESB), Parliament

- Industry in the context of the Industrial Alliance on Processors and Semiconductor Technologies

- Impact assessment and studies to review the Chips Act will be launched shortly

- Input from Court of Auditors report, mid-term assessment Horizon Europe, ...

□ Need to show clear results and impacts!

# Thank you