### Chips JU Initiative calls 2023 and 2024

Yves Gigase Head of Programmes 21 February 2024

# The 3 pillars of the Chips Act

#### European Semiconductor Board (Governance)

#### Pillar 1

#### **Chips for Europe Initiative**

- Initiative on infrastructure building in synergy with the EU's research programmes

- Support to start-ups and SMEs

#### Pillar 2

#### **Security of Supply**

First-of-a-kind semiconductor production facilities

#### Pillar 3

### Monitoring and Crisis Response

- Monitoring and alerting

- Crisis coordination mechanism with MS

- Strong Commission powers in times of crisis

**Chips JU**

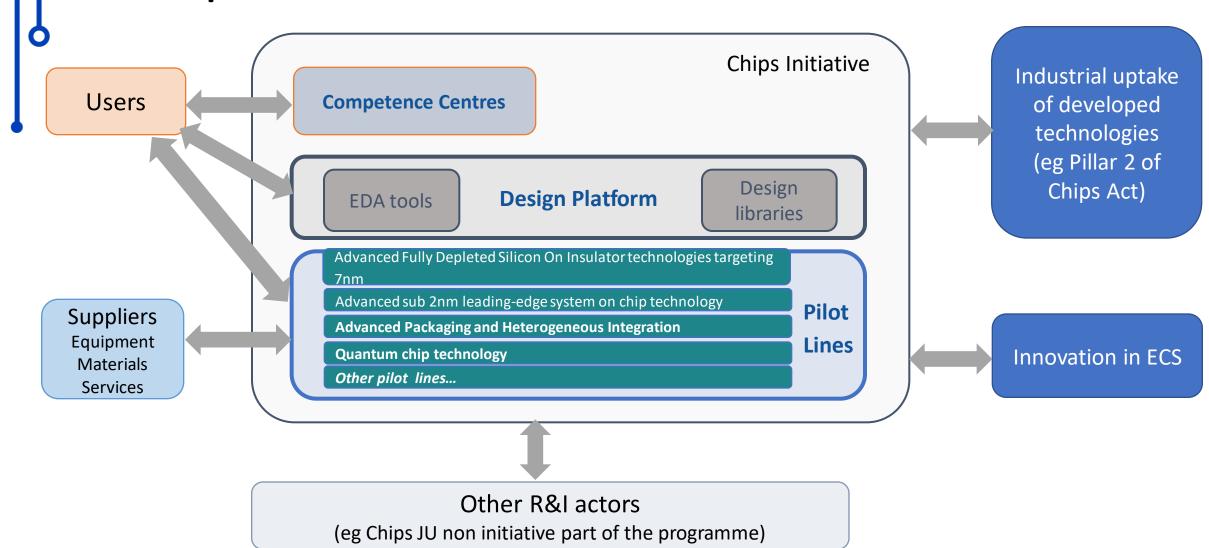

### Chips JU objectives

- a) Reinforce EU strategic autonomy in electronic components and systems

- b) Establish EU scientific excellence and innovation leadership

- c) Ensure that components and systems technologies address Europe's societal and environmental challenges

- d) Pilot lines

- e) Design platform

- f) Competence centers

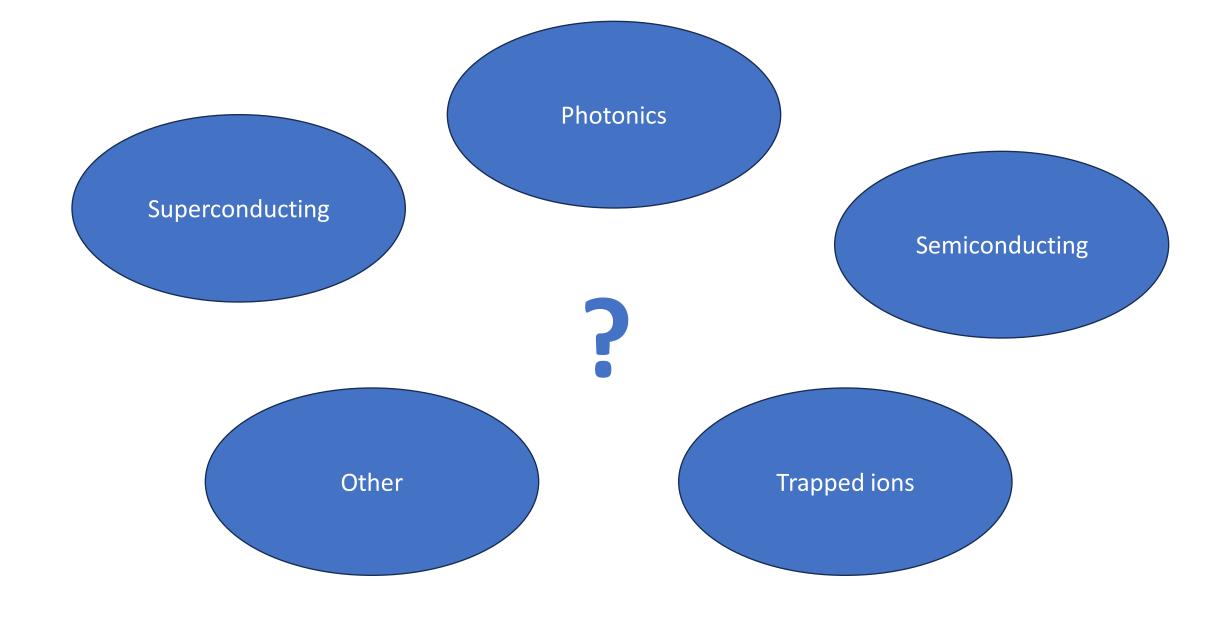

- g) Quantum chips technology

- h) Skills

→ INITIATIVE

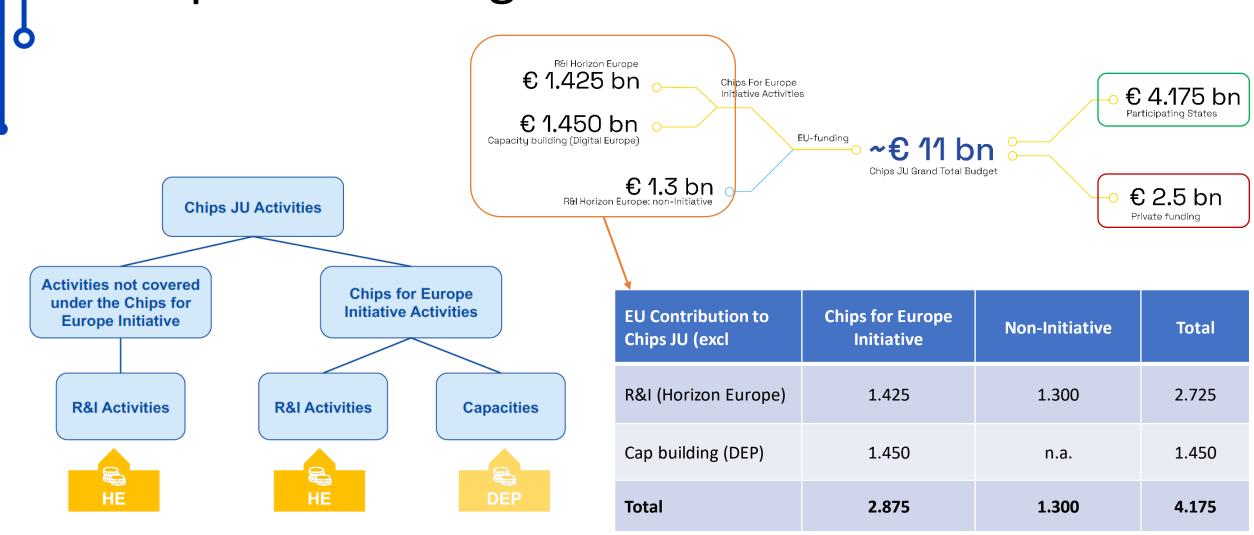

# Chips JU Funding

## Chips JU: From Lab to Fab

## Call Chips 2023: First calls opened in Dec. 2023

| Call        | Topic                                                                                 | Max EU<br>Contribution | Participating States' contribution | Total      |

|-------------|---------------------------------------------------------------------------------------|------------------------|------------------------------------|------------|

| Chips-CPL-1 | Pilot line on advanced sub 2nm leading-edge system on chip technology                 | 700 MEUR               | 700 MEUR                           | 1,400 MEUR |

| Chips-CPL-2 | Pilot line on advanced Fully Depleted Silicon On Insulator technologies targeting 7nm | 420 MEUR               | 420 MEUR                           | 840 MEUR   |

| Chips-CPL-3 | Pilot line on advanced Packaging and Heterogenous Integration                         | 370 MEUR               | 370 MEUR                           | 740 MEUR   |

| Chips-CPL-4 | Pilot line on advanced semiconductor devices based on Wide Bandgap materials          | 180 MEUR               | 180 MEUR                           | 360 MEUR   |

- Closing date February 29, 2024. Complex call starting with a Call for Expression of Interest leading to a Hosting Agreement and a Joint Procurement Agreement, and calls for related HE and DEP grants.

- Expected project start in 2Q 2024.

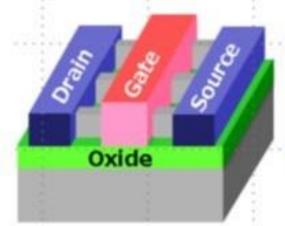

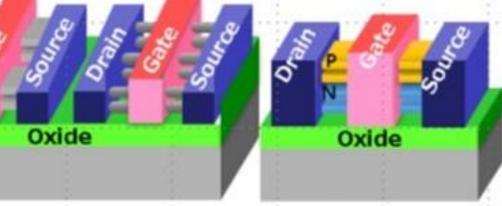

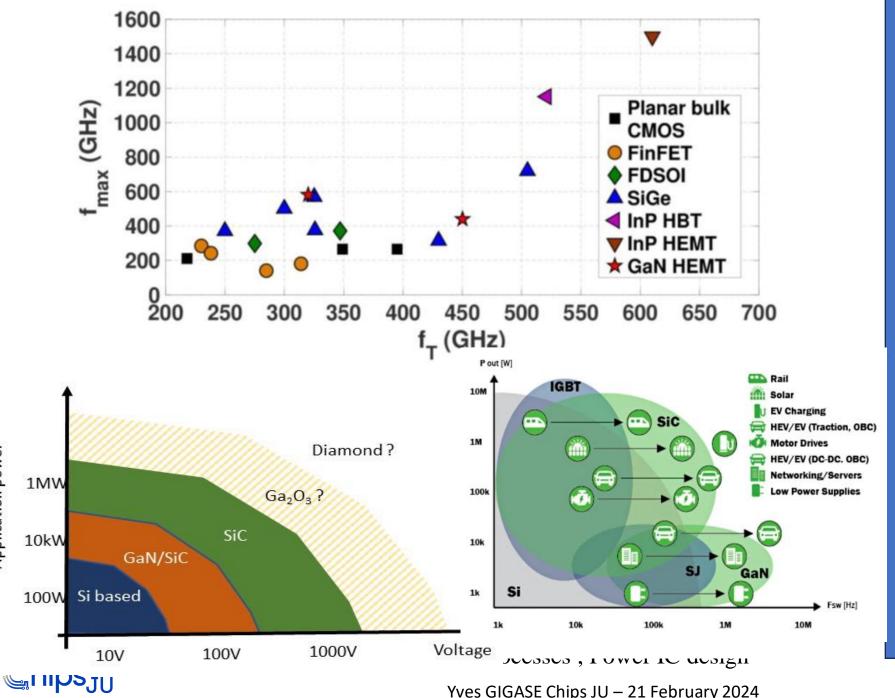

# Introduction: scaling scenario for device architectures

→ scalability, density Floating body Fully depleted substrate planar SOI-Bulk-GAA **FinFET FinFET FDSOI** Bulk **PDSOI** Gate UT-cSi UT-BOX vertical lateral 7 **GAA-NWFETs:** can be build in a lateral vs. vertical configuration BOX ☐ doping strategies: inversionmode (IM) vs. junctionless (JL)

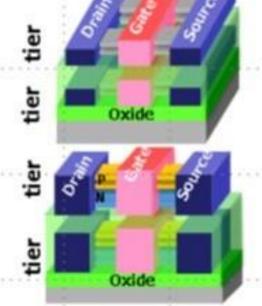

IRDS roadmap 2022 Executive summary

Figure ES56 Practical migration of transistor structure from FinFET to GAA to fully vertical

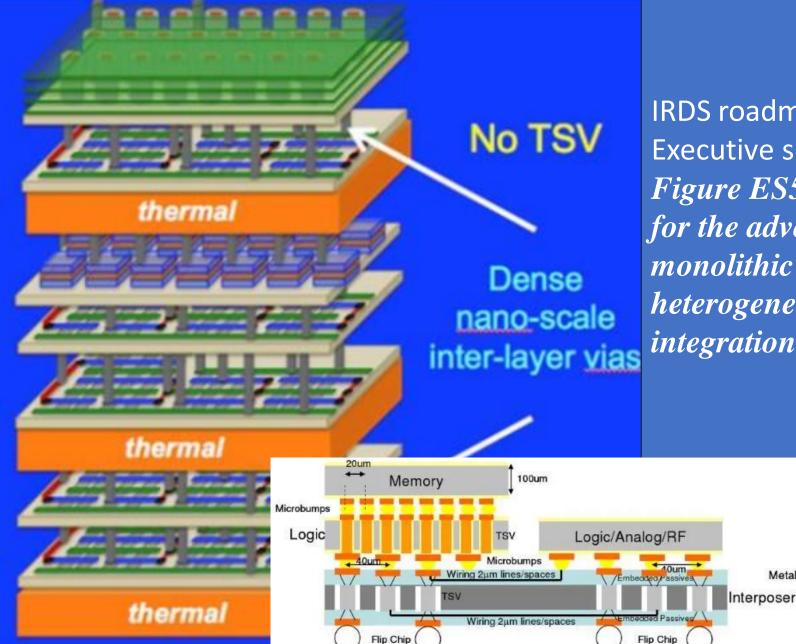

### >2020: 2.5D/3D fine-pitch assembly + stacking

FinFET 2011-2022 Lateral GAA 2022-2037

CFET 2028-2037

Increasing drive by taller fin

Better channel control for

better perf-power

- Increasing drive by stacked devices

- Better channel control

- Reduced footprint stdcell

- Increased stacking

- Reduced PN proximity

- Reduced footprint stdcell

3D VLSI 2031-2037

Sequential heterogenous integration/fine-pitch stacking (e.g., logic, memory, NVM, analog, IO, RF, sensors)

IRDS roadmap 2022 Executive summary Figure ES57 Change in the MOSFET device architecture from the 2D planar through 2.5D FinFET to 3D monolithic VLSI with GAA

3D Resistive RAM Massive storage

1D CNFET, 2D FET Compute, RAM access

> STT MRAM Quick access

1D CNFET, 2D FET Compute, RAM access

1D CNFET, 2D FET Compute, Power, Clock

IRDS roadmap 2022 **Executive summary** Figure ES58 Planning for the advent of monolithic heterogeneous integration

Metal

\_Dielectric

Land pad

Application power

IRDS roadmap 2022 Executive summary

Figure ES46 Silicon device limitations to operate above 400 GHz

### Some general outcomes common to all PL

- Expanding the European user base of this technology and build a community of interest around this technology.

- Access to those advanced technologies, preferential for SMEs and Start-ups with the support of the Competence Centers to be started by the Chips JU.

- Early research **Process Design Kits for the design platform** and support to the design platform for those kits.

- A collaboration with the other pilot lines established under the Chips JU, creating a strong networked European environment for advanced chip technologies.

- > Training and skill development

# Call Chips 2024: Initiative part

| Call             | Topic                                                                                                                                                                                                                                                                                                                                                                                           | Max EU<br>Contribution |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Chips-2024-CDP-1 | Design platform. A cloud-based virtual platform that will enable users, particularly academia, start-ups and SMEs, to design and develop their chips                                                                                                                                                                                                                                            | 330 MEUR               |

| Chips-2024-CPL-5 | Additional pilot line(s);                                                                                                                                                                                                                                                                                                                                                                       | 180 MEUR               |

| Chips-2024-CQC-1 | Quantum chips technology (preparatory action for a pilot line)                                                                                                                                                                                                                                                                                                                                  | 30 MEUR                |

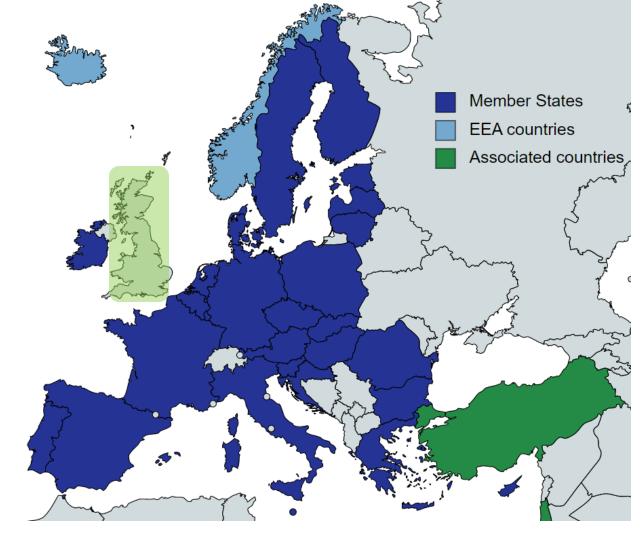

| Chips-2024-CCC-1 | Competence centres. The centres are tol provide access to technical expertise and experimentation in the area of semiconductors, helping companies, SMEs in particular, to approach and improve design capabilities and developing skills.  Max 1 per Participating State, funding up to 1 MEUR/yr from the EU for 4 years, to be matched nationally. Restricted call after national processes. | 116 MEUR               |

| Chips-2024-CCC-2 | European Network of Chips Competence Centres (CSA)                                                                                                                                                                                                                                                                                                                                              | 4 MEUR                 |

### WHAT WOULD HELP?

**Ambition**: to provide start-ups, SMEs and other users a design environment similar to what is expected at larger companies through the aggregation of demand